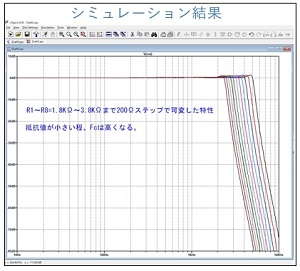

| 儅僉僔儉偺MAX294傪俀抜僇僗働乕僪偵巊梡偟偰嶌惉偟偰偍傝傑偡杮IC偼100攞偺僋儘僢僋廃攇悢丄偮傑傝僇僢僩僆僼亖3.0KH倸偵愝掕偟偨偄応崌偼僋儘僢僋偼侾侽侽攞偺300KH倸偱嬱摦偡傟偽椙偄僋儘僢僋廃攇悢傪壜曄偟帺桼偵僇僢僩僆僼廃攇悢偑愝掕弌棃傞丅MAX294偼亇5V嬱摦弌棃傑偡偑丄懠偺7000僔儕乕僘IC偱偼5V扨揹尮嬱摦偲側傝丄俢亅儗儞僕/俽俶傪峫椂偡傞偲墦椂偟偨曽偑傛偄偺偱偼丠帺嶌婡偱偼2抜僇僗働乕僪偱偼側偔1抜峔惉偱巊梡偟偰偄傑偡丅栤戣偲側傞偺偼丄僋儘僢僋惗惉朄偱偡丅婎弨僋儘僢僋偐傜暘廃偟偰暘廃斾傪壜曄偡傞曽朄偲丄俹俴俴傪峔惉偟暘夝擻亖10俲Hz偲偟偰僇僢僩僆僼廃攇悢亖100俫倸僗僥僢僾偱壜曄偡傞曽朄偑偁傞偑奺惢嶌婡婍偼慜幰偺庤朄偱峴偭偰偍傝傑偡丅枖屻幰偺庤朄傕扨昳嶌惉偟傑偟偨偺偱徯夘偟偰偍偒傑偡丅 |

夞楬恾僼傽僀儖 夞楬恾僼傽僀儖 |

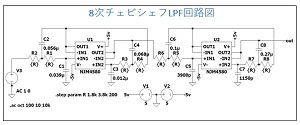

| Fc=3.0KHz偺幚應摿惈 |

|

尨敪僋儘僢僋暘廃偐傜偺嶌惉

憲怣婡乛庴怣婡嫟偵僔僗僥儉尨敪僋儘僢僋偼俀俈俵俫倸偱峔惉偟偰偍傝丄偙傟傪尦偵暘廃斾傪壜曄偟偰僋儘僢僋傪惗惉偡傞丅偙偺曽幃偼暘廃斾偑妱傝愗傟側偄応崌偑敪惗偡傞丄椺偊偽僇僢僩僆僼亖3.0俲俫倸偺応崌偼僋儘僢僋亖300俲俫倸偑昁梫丄27俵Hz乛90亖300俲俫倸偙偺応崌偼僺僢僞儕偱偡丄僇僢僩僆僼亖3.1俲俫倸偺応崌偼僋儘僢僋亖310俲俫倸偑昁梫丄27俵俫倸乛87亖310.34俲俫倸偲側傝丄幚僇僢僩僆僼亖3.1034俲俫倸偲側傞丅僇僢僆僼廃攇悢偼100俫倸暘夝擻偱嵟彫岞攞悢傪偲傝壗傜栤戣柍偄丅俠俹倀惂屼偱偼俢侽乣俢俈偵暘廃僨乕僞乕傪僙僢僩偟俴俷俙D偱庢傝崬傓丄俠俹倀偱偼側偔丄俽倂愝掕偱傕壜擻偱偡丅 |

夞楬恾僼傽僀儖 夞楬恾僼傽僀儖 |

俹俴俴偵傛傞嶌惉

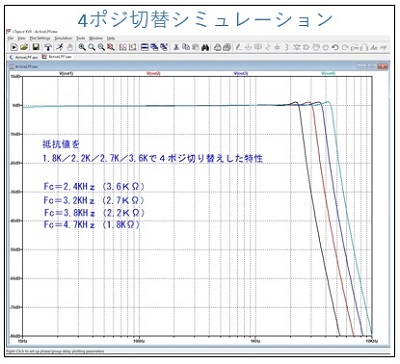

偙偺曽幃偺棙揰偼丄俀寘偺僨僔儅儖俽倂傪巊梡偡傞偙偲偵傛傝丄娙扨偵愝掕偑弌棃丄昞帵傕妋擣弌棃傞丄枖僋儘僢僋廃攇悢傕僺僢僞儕偲惗惉弌棃傞丅僇僢僩僆僼廃攇悢亖100俫倸暘夝擻偱愝掕偟偨偄応崌偼100俫倸倃100攞亖10俲Hz偺婎弨僋儘僢僋偑俹俴俴夞楬偵昁梫偲側傞丅奺婡婍偺帺嶌婡婍偼丄尨敪怳僋儘僢僋乮27俵Hz)偼俧俹俽偐傜嶌惉偟偨奜晹婎弨僋儘僢僋10俲Hz偐傜儘僢僋偝偣偰偄傞偨傔丄偙偺10俲俫倸婎弨僋儘僢僋傪偦偺傑傑巊梡偡傞偐丄僔僗僥儉尨敪乮27俵Hz)偐傜1/2700暘廃偟偰10俲俫倸傪庢傝弌偟偰巊梡偡傞偐丄偄偢傟偵偟偰傕昁梫偲偡傞俹俴俴偺僗僥僢僾暘夝擻偵傛傝堎側傝傑偡丅俠俹倀惂屼偱偼俙0乣俢侽乮暘廃斾堦偺寘乯丄偲俙1乣俢1乮暘廃斾廫偺寘乯傪愝掕偡傟偽傛偄丄僨僔儅儖俽倂偱偼侽乣俋偺僨僔儅儖俽倂傪堦偺寘偲廫偺寘偺俀働強偵巊梡偡傞丄俽倂偺昞帵偑僇僢僩僆僼廃攇悢偲側傞丄椺偊偽僇僢僩僆僼廃攇悢亖3.0俲俫倸偺応崌偼丄廫偺寘俽倂亖3丄堦偺寘俽倂亖0偲側傞丅僇僢僩僆僼亖3.0俲俫倸偱偼昁梫僋儘僢僋亖300俲俫倸丄愝掕暘廃斾亖300俲俫倸乛10俲Hz亖30偲側傞3.1俲俫倸偺応崌偼310俲俫倸丄愝掕暘廃斾亖310俲俫倸/10俲俫倸亖31偲側傞丅 |

夞楬恾僼傽僀儖 夞楬恾僼傽僀儖 |

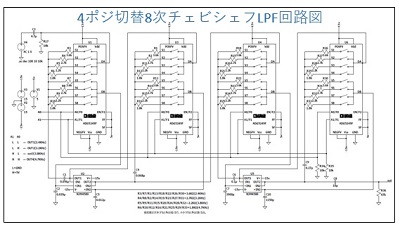

| 俹俴俴曽幃偺俽俠俥惂屼婎斅 |

|

丂丂丂丂丂丂

丂丂丂丂丂丂

夞楬恾僼傽僀儖

夞楬恾僼傽僀儖

夞楬恾僼傽僀儖

夞楬恾僼傽僀儖 夞楬恾僼傽僀儖

夞楬恾僼傽僀儖