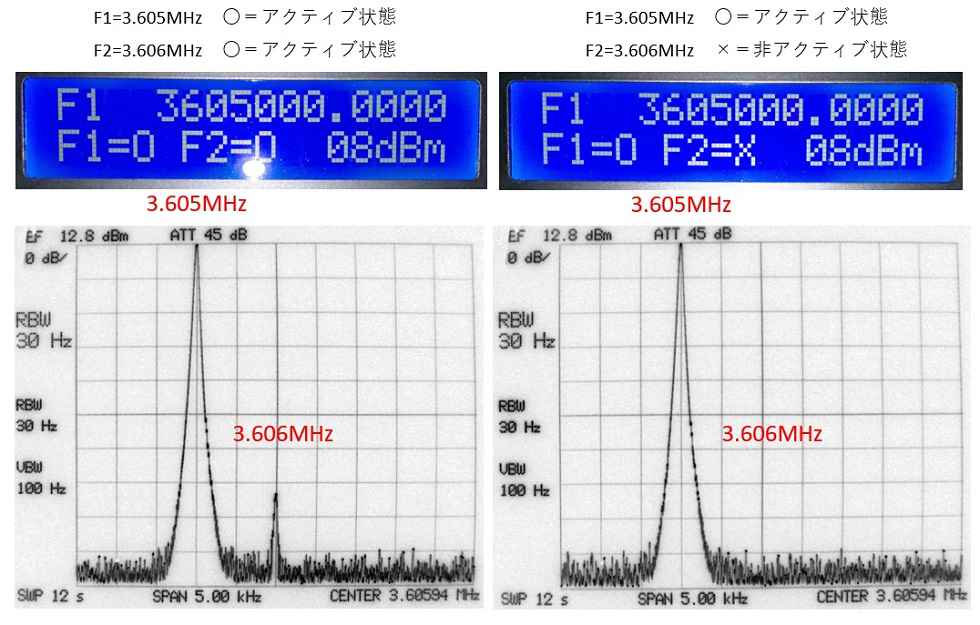

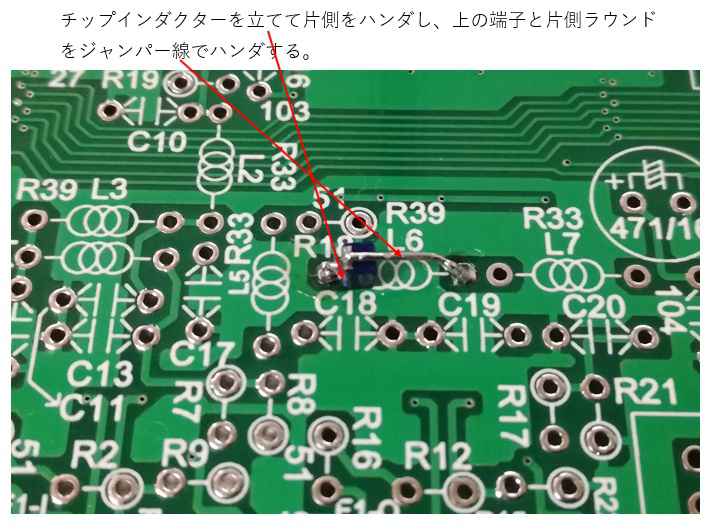

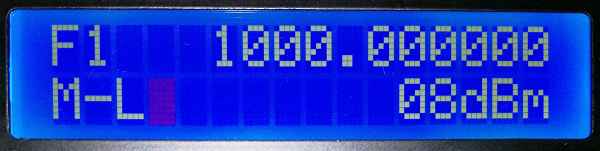

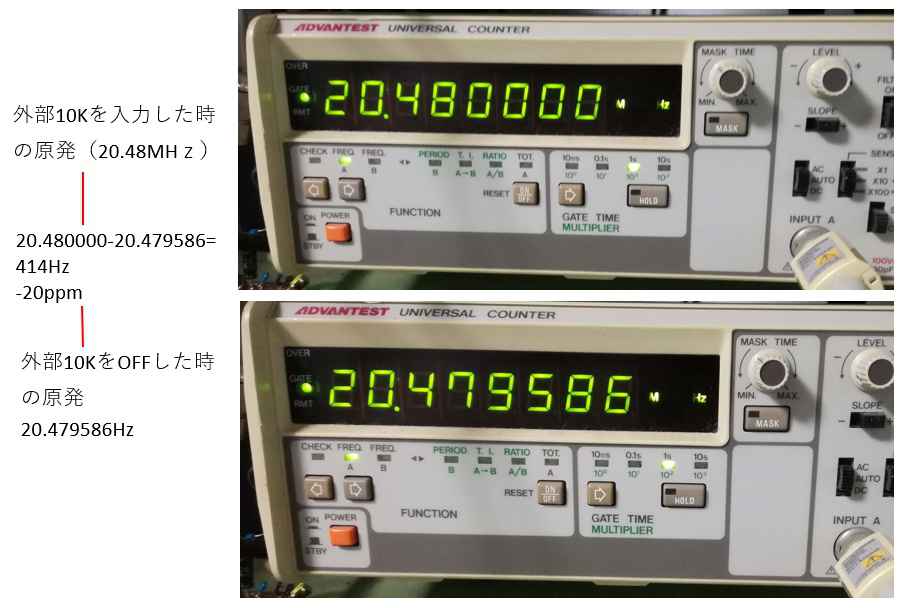

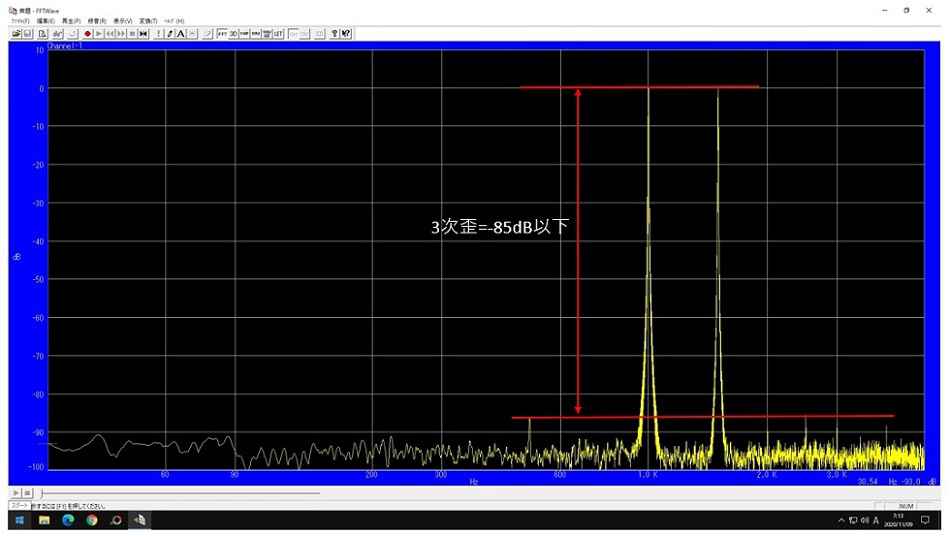

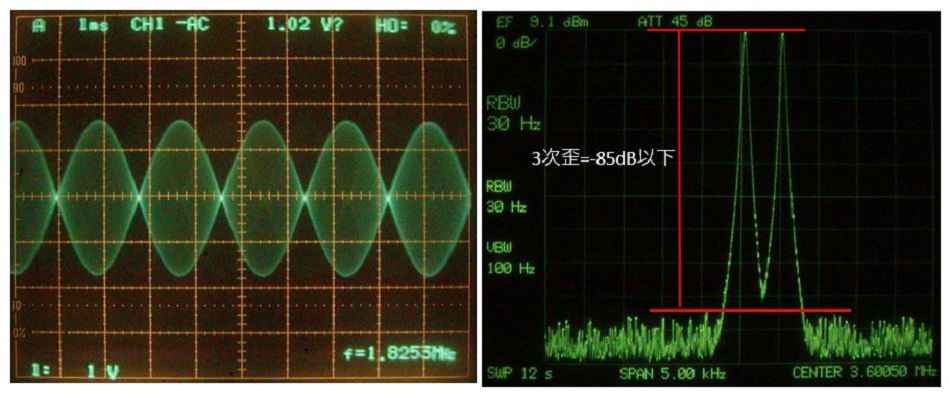

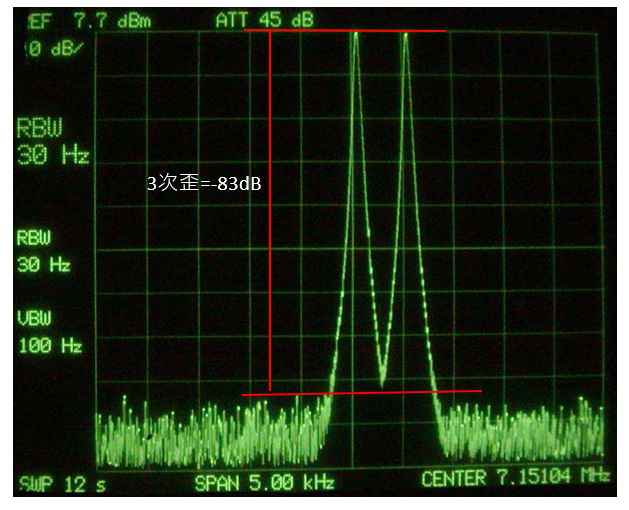

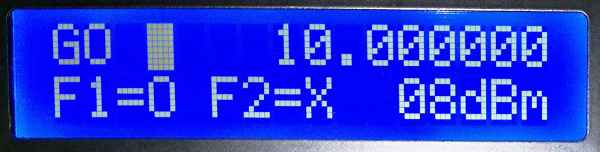

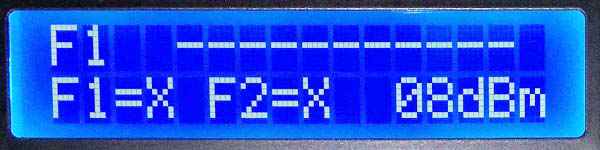

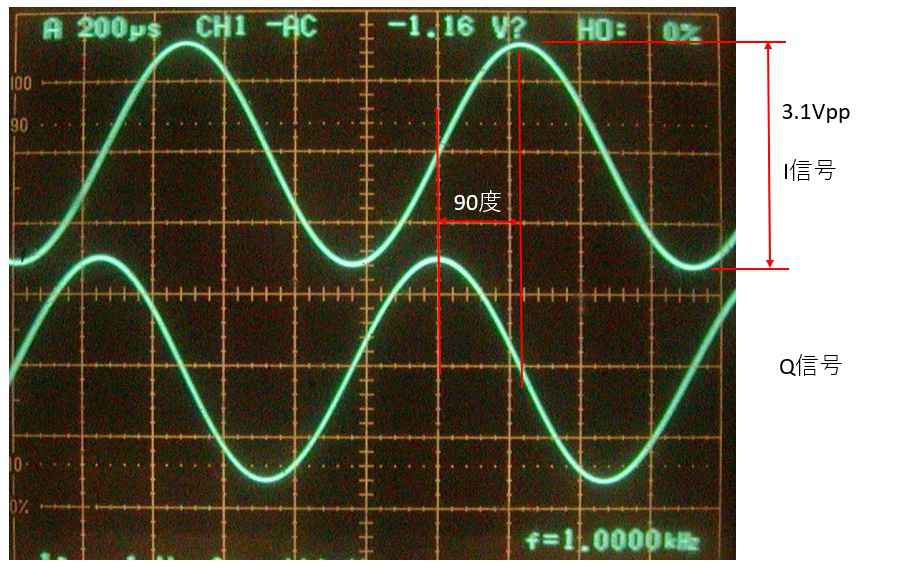

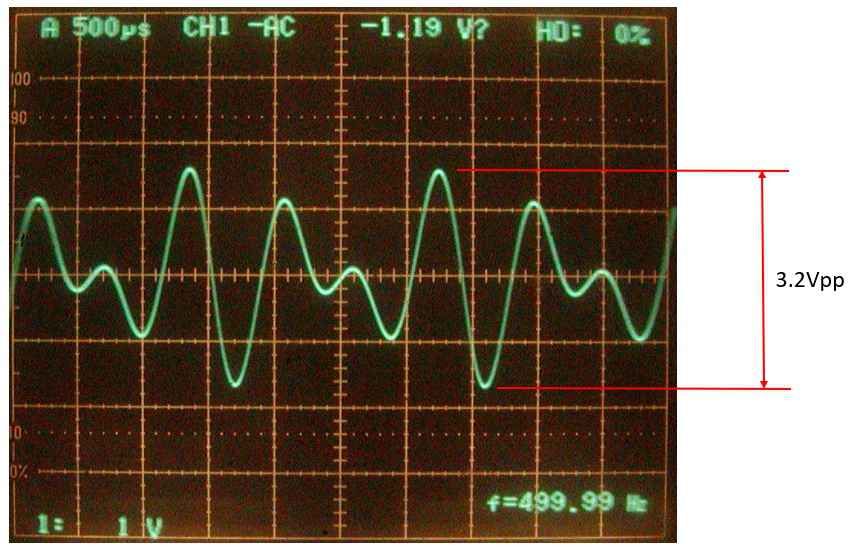

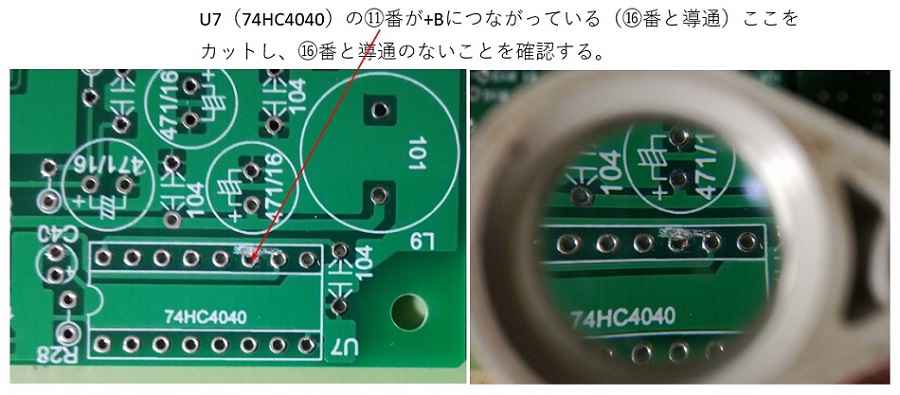

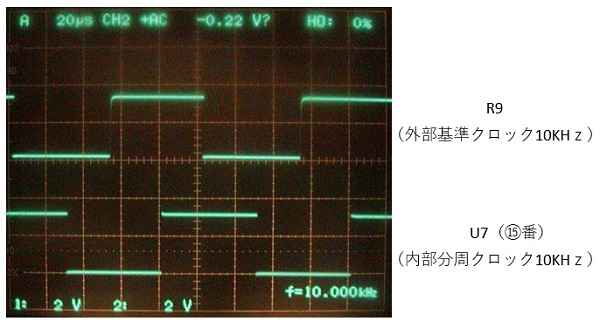

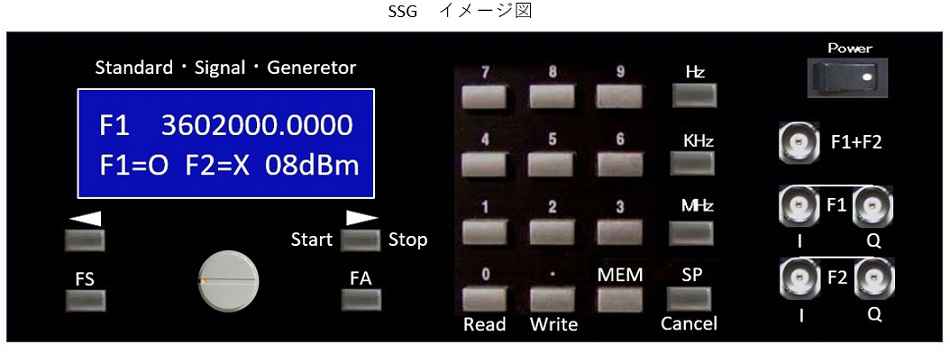

【最終情報】 main基板のR23=181→221に回路図の修正が出来ていなかった。 最終回路図と取扱 最終回路図(210103) 取扱説明書 【ケースが入荷し組み上げて完成】 2020/12/25日    【使用上の注意点】 基本的には2個の発振器を内臓しており、通常のSGとしての使い方は1つの発振器を使用するケースが多い、1つの信号出力として使用する場合は、他方の発振器は×=非アクティブに設定して使用すること。 2個同時に〇=アクティブ状態で使用する場合は(F1+F2)端子から2信号出力として使用すること。2個同時に〇=アクティブ状態にして、F1又はF2出力から使用するとクロストークがあり、端子にもよりますが-70dB以下ではあるが、F1又はF2からの使用では1信号として出力させて使用すること。下の波形はF1=30605MHz、F2=3.606MHzを出力させ、両方=〇状態と、F2のみ=×状態にしたものを比較したものでF1出力端子で観測したもの。  【スタートして11/14までに修正となった項目のまとめ】 ① U7(⑪番)をパターンカット(生基板状態)し装着後に⑪番=GND配線する。下記【調整・動作確認】の⑧を参照。 要因=U7(カウンター)がスタート出来ない。 ② Display基板のR2=R3=103→393 要因=秋月のロータリーエンコーダーのチャタリングバラツキが大きい。 ③ main基板のR10=R32=272→222、 R2=R12=R31=R44=561→681 要因=レベル設定の変更。 ④ CPUユニットのチップコンC1=C5=104→105、 タンタルC2=C4=C6=22/16→47/16 要因=支給部品としてまとめたい。 ⑤ main基板のL3=L6=L11=L14=0.39uHはチップタイプしか調達出来なかったため、少し取付に工夫がいる。  ①としてmainの回路図修正 main回路図1114 その他は今までの回路図1108に反映されている。 【操作マニアル】 今までの説明で基本的な操作は殆ど含まれているので不要と思うが、何点かを説明しておく。 万一、操作中に挙動不信で正常とならなくなった、電源OFF/ONしても異常となった場合は、”←”キー + ”→”キー を押して電源SW=ONして下さい。初期化します。 ① メモリー機能 ノーマルモード時に”MEM”キーを押すことによりメモリーの読み出し又は書き込み動作を行うモードに入る。  メモリーには計18チャンネル分あり、M1~M18と表現してもよかったが、AFPSNの位相調整時に便利なように、M-L列=9 チャンネル分、M-U列=9チャンネル分 で計18チャンネル分設けている。L列の箱又はU列の箱に読み書きするには”←”Left キーでL列の箱か、”→”RightキーでU列の箱かを選択する。例としてL列の箱で行ってみる、”←”Leftキーを押す。  ”→”Rightキーを押した場合は、U列の箱になる。  M-L列の箱である。この箱に1~9チャンネル分の周波数を書き込み/読み出しが出来る。”1”を押してみる。  これでM-L1の周波数を読みだすのか、書き込むのかです。読みだす場合は”0”(Read)キーを押す。  ”Read”文字が出て、メモリーされていた周波数が出力され、ノーマルモードとなる。  この場合、L列-1段目のポール周波数=5.6782Hzが出力される。メモリーする周波数はF1/F2いずれの周波数でもOK。 次に、メモリー書き込み動作を行ってみる。チャンネルを指定したところまでは、上の手順と同じ。  ここで、読み出しするのか、書き込みするのか、書き込みする場合は”.”Writeキーを押すが、その前にノーマルモードで F1の周波数かF2の周波数か書き込みたい周波数をセットしておくこと。  書き込みされると”Write”文字が出て、ノーマルモードとなる。 つまり、AFPSNのポール周波数を出す場合は、例えば8段で一般的に調整する時は、L列の1段目~8段目の周波数とU列の 1段目~8段目の周波数を、その段毎に周波数設定していた。又、1個の発振器で行っていた、測定ポイントの繋ぎ変えは 仕方ないとしても、周波数数値を度に入力するのはミスの要因となる。 このメモリー機能を使えば、例えば、M -L列1~8 の箱にL列の1段目~8段目の周波数をF1で書き込んでおく、M -U列1~8の箱にU列の1段目~8段目の周波数をF2で書き込ん でおく。こうすると調整時に入力(L列とU列)の2つをブリッジさせておく必要もなく、F1出力=L列入力へ、F2出力=U列 入力へ接続しておき、後はメモリーの読み出しだけで調整が出来る。 ② 出力レベル調整 ”FA”キーを押すと、出力レベル値へカーソルが移動します。この状態でロータリーエンコーダーを回すと-30dBm~+8dBm まで1dBステップで可変出来ます。 ③”←”Leftキーと”→”Rightキーの使い方 のマルモードと可変したい桁にカーソルを移動させ、エンコーダーで周波数のUP/DOWNが出来ます。 ④ テンキーで周波数入力中に希望としない数値を誤って押した時には、”SP”(Cancel)キーを押せば元に戻ります。 【測定結果の追加】 ① 原発(20.48MHz)が外部10KHzにロックインした時とアンロック状態の時の周波数偏差。  ② I/Q信号の位相偏差 10Hz~3KHの確認はしたが、AFPSNで使用する帯域(30KHz)10Hz~30KHzでの確認をしてみる。スイープ設定で Start=10Hz、Stop=30KHz、Time=20秒 をして確認して測定してみると位相エラー=0.01度 これは恐らく位相計の 誤差が出ているような気がする。  【測定結果】 ① (F1+F2)の出力端子信号 ・オーディオ信号(1KHz+1.5KHz)の2信号   ・RF信号(3.6000MHz+3.6005MHz)のRF2信号   ・RF信号(7.1500MHz+7.1505MHz)のRF2信号  ② スイープ動作の確認 ”SP”キーからはじまる。”SP”キーを押す毎に、”Start周波数”→”Stop周波数”→”スイープタイム”→”ノーマルモード”と 切り替わっていく。”ノーマルモード”以外のどこかで”→”右矢印キーを押すことによりスイープ動作がスタートします。 途中、再度”→”キーを押すとスイープを停止します。”→”キーではスタート/停止の繰り返しとなります。スイープ状態 から脱出してノーマルモードへ移行するには、停止中に”SP”キーを押して”ノーマルモード”まで移行させる。 例えば Start周波数設定---10Hzに設定  Stop周波数設定---3KHzに設定  スイープタイム設定---10秒に設定 秒のキーは”Hz”キーを押す  ”→”左矢印キーでスイープ動作がスタートする。  Start周波数=10Hz Stop周波数=3KHz スイープタイム=左側=10秒設定、右側=20秒設定した時の動画で右側 は真下に位相計、右のメーターは関係ない。赤針=入力レベルで、自作の位相計では3Vpp入力を理想としているため出力 =07dBmに設定し、F1のI出力とQ出力を位相計に入力し位相差を確認した。右側の動画、10Hz側のリターンでノイズに より位相針が振れるが、3KHz側は発生していないので、3KHz→10Hz間での位相誤差を確認したが、殆どエラーはなし 位相計のレンジは、±0.1度である。   【調整・動作確認】 ① Displayユニットの消費電流確認、CPUユニットを装着した状態で+5V単電源を供給する--- 約20mA ② LCDのコモン調整--- 白文字が一番見え易いようにVR1を調整する。 ③ +5V印加時のLCD表示。  ④ 各キーを押しての反応をチェックする。 ⑤ Mainユニットの消費電流確認 ±5Vの3端子とPQ3Rは取り付けないで、ベンチ電源で+3.3V/±5Vを接続し電源供給するとLCD表示は上の状態で、3.3V= 0.42A、+5V=0.08A、-5V=0.06A 近傍となる。 ⑥ Main基板のオフセット調整 上の表示状態で、”FS”キーを0.5秒以上押しつづける、するとF1=アクティブ状態から非アクティブ状態に変わりF1=X、F2= Xとなり、両信号が非アクティブ状態となります。  この状態での3.3V=0.15Aで、±5V=同じ 3.3V電流は最大=0.9A 近傍となることがある。 各出力端子でのオフセット調整 ⑦ 各出力端子の動作確認 F1、F2共にアクティブ状態にする。”FS”キーは押す毎にF1/F2と切り替わります。又、0.5秒以上押しつづけるとON/OFFを 繰り返します。  各出力端子で指定された周波数が3.1Vpp出ていること、又、I/Q信号間は90度の位相シフトがあること。  (F1+F2)出力端子 1KHz+1.5KHzの2信号  ⑧ 外部基準クロック(10KHz)ロック動作の確認 <修正が必要なケ所があります> ・U7(74HC4040)の⑪番(CLEAR端子)が+Bラインに配線されています。この端子はL(GND)する必要があり、パタ ーンカットし、IC装着後に⑪番をGNDへ配線します。 ・R25(デジトラの出力抵抗)の部品挿入は、シルク印刷の逆方向へ挿入して下さい。動作には関係ないが、確認ポイント として使用するため。  外部基準クロックへロックインする動画、入力OFF/ONしています。ONすると即座にロック。   【製作】 製作手順書 【設計】 回路図1108 部品表1108 過去の経験から極力コネクタ(コネワイヤー)は無くすことが望ましい。電源ユニットは独立させずメイン基板内に一体化し、AC100Vの供給のみとする。表示ユニットとメインユニットの結合はコネワイヤーではなく、FFCケーブルで検討してみたが、どうしても高すぎる(長さの関係で標準品に出来ない) よってこの度もコネワイヤーでの結合にした。 mainブロック ① 使用するDDSの機能条件として ・30MHzX6倍以上のクロック駆動が出来ること。 ・I信号/Q信号が独立して出力出来 ること。 ・周波数レジスタ=48bit有していること。 ・SSOPよりファインピッチでないこと。 によりAD9854を選定。 ② システムクロックとしては原発=20.48MHzX9=184.32MHz駆動とする。原発を20.48MHzとした理由は、20.48MHz はVCXOとして外部基準クロック10KHzでロックをかける、この時、10KHzの2のN乗倍で30MHzに最も近い周波数 が20.48MHzである。20.48MHz/2^11=10KHzとなり、1個のカウンターでデューティーも完全50パーセントで出力 されます。 ③ 原発のロック回路は、20.48MHzのVCXO出力を74HC4040で1/2048分周して10KHzを作成し外部基準クロック10KHz をQ1で駆動した10KHzの2つの信号をU5(7SH86)のX-ORで位相比較し④ピンに2倍の周波数(20KHz)で出て来る。これを CRでフィルタリングしてVCXOの制御端子へ供給する。外部基準クロック10KHzを抜くとU5の④ピン出力にはU7で分周された 10KHz(デューティー50%)がそのまま出力され、VCXOの制御電圧としてはVcc/2の電圧が供給され、20.48MHzのアンロッ ク周波数のズレ分としては非常に小さく、インターナルクロックだけでも用途によっては十分可能である。本回路の電源電圧は 全て3.3V駆動です。 ④ 電源電圧としては、AD9854=3.3V、VCXO=3.3V、CPU・カウンター等=2.7~5V であるため3.3V1本も可能であったが 出力アンプを+10dBm得るために±5Vが必要となる。又、購入したLCD=3.3V品ではなく5V品であったため、電源回路はト ランスの2次巻線がAC6V-2巻線を使って、1巻線=+3.3Vとして、もう1巻線=±5Vとして使用。ちなみに、消費電流としては 3.3V=最大1A、+5V=80mA、-5V=60mA消費する。 ⑤ DDS出力信号はI/Q共に35MHzの7次LPFを経由し電流帰還型の広帯域オペアンプで50Ω出力の+8dBmまで増幅している 出力信号としては0.000001Hz(1uHz)から出力させるため、C結合を行うことは出来ない。DDSは+3.3V単電源ですから 出力信号としてはプラスのオフセット電圧を有している、そこで各オペアンプ回路でバイアス=±0Vとなるように472(502) の半固定VRで調整する。 ⑥ F1+F2信号は任意の2信号が出力出来ます。出力レベルは、例えばF1=+8dBm、F2=+8dBmに設定してあればF1+F2の 出力端子ではVpp=3.1Vppであるが、dBmでは各F1/F2=8dBm-5dBm=+3dBmとなる。 ⑦ コントロールラインに使用しているラダー抵抗は、CPU=+5VでDDS=+3.3Vであるため、5V→3.3V変換するための物です。 Displayブロック ① この種のLCDは過去何度も使用しているが、COM(③番)端子、これはLCDのコモンバイアスを調整するもので、過去LCDの 文字が見えない不良品じゃと言った話を聞きましたが、VR1で一番見え易い状態にセットする。 ② キーマトリクスは静的なものではなく動的に動作させていますから小細工は出来ません。 ③ この度のロータリーエンコーダーは秋月の安い機械式を使用します。そのためハード的にもチャタリング吸収回路を入れてお ります。秋月には2種類(足ピッチの広い物と狭い物)あり、端子が共通ではないため、JP1~JP4でどちらにも対応出来るよう にしています。 【SSGの仕様】 ① 独立した信号源2個(F1・F2)を出力し、両方をアクティブにした場合は2信号として出力出来る。 ② 出力端子は、F1/F2/F1+F2で、F1とF2は各I・Q信号も出力される。 ③ 出力周波数は、0.000001Hz(1uHz)~32MHz 外部基準クロック入力=10KHzに対応。 ④ 出力レベルは、-30dBm~+8dBm 特別な減衰器は使用しておらずDDS機能で制御、-30dBmとしたのは受信機のANT 端子で-23dBm=S9+50dBであるため、ここまでの設定であればそのままでOK、これ以上減衰させるには外部ATTを付け る必要がある。又+8dBmとしたのは、我々自作のAF-PSNの位相調整器は入力レベル=3Vpp(+7dBm)入力で測定して おり最大出力=+8dBmとした。又周波数精度も小数点以下3桁の周波数精度が要求される。 ⑤ スイープ機能 Start周波数・Stop周波数・スイープ時間を設定し永遠に繰り返しが出来る。 ⑥ メモリー機能 計18チャネル分確保出来るが、これはAF-PSN(各段のポール周波数)の調整時にポール周波数の度に入力する必要があり しかも小数点以下3桁入力時には入力ミス等もあり、これを防ぐためU列/L列の各ポールに周波数メモリーしておき読み出せ るようにする。  【デバイスの選定】 ① 発振源はDDSで行うが、DDSに要求される項目として、DACのbit数/周波数レジスタのbit数/I・Q信号が同時出力出来る等 であるが、DAC=14bitで周波数=48bitとなると、かなり限定され、しかも形状がBGAタイプとなりI・Qの同時出力は困難と なる。よって、DAC=12bit/周波数=48bit/I・Q出力可能なDDS(AD9854)を選択することとした。これは消費電力が大 きくQFP80とピン数は多いが、過去の自作に使用経験があり、これを選択することにした。しかし、これ等の調達は国内では かなり高価であり中国からの調達をトライする。 ② 出力信号の処理としての高周波オペアンプは、AD8009(電流帰還タイプ)を使用、電源電圧=±5Vであるため出力レベルは 限定される。 ③ 表示器としてはキャラクタLCDを使用するが、秋月等では¥800するが、Amazonに同程度のサイズ仕様で¥185であり即決定。 実際に使用してみると秋月品はブルーバックがマゼンタぽく、マルツパーツ品はマゼンタぽさは無く綺麗だが高い、Amazon品 は勿論、マゼンタぽさも無く綺麗で安い。 【製作のいきさつ】 ① HP社の標準信号発生器(3325)が壊れた、エラー表示となりトライしたものの修理出来ず。復元したとしても特に奥行があり 重く便利性を欠く。 ② 以前製作した”3DDS”は万能型を意識し各無線機製作のキャリア用としてつくり、勿論、SSGとしても使用出来るが、使用した CPUが古くバージョンアップが不可である。 ③ 測定器用としての信号発生器を意識し、オーディオ(超低域)から高周波(HF)まで連続発振が出来、特に発振周波数の精度 には基準クロックとして使用出来るマイクロヘルツ精度。小型で軽いSSGが欲しい。 |